-

Virtual Memory대학/컴퓨터구조 2023. 6. 13. 22:23

Disk를 Virtual Memory로 사용하기 위해 메인 메모리를 캐시로 사용한다.

Virtual address는 page table을 통해 Physical address로 변환되는데 이 과정을 살펴보자.

디스크는 데이터를 페이지 단위로 관리하기 때문에, 가상 메모리 역시 페이지 단위로 관리된다.

그 페이지 내부에서 특정 데이터를 찾기 위해 offset를 지정하게 되고,

나머지 부분은 페이지의 인덱스를 나타내게 된다.

Valid가 0이면 해당 주소에 해당하는 데이터가 속한 페이지는 디스크상에 존재하는 것이고,

1이라면 메인 메모리에 캐싱된 상태이다.

하지만, CPU입장에서는...

- 페이지 테이블에 접근

- 페이지 테이블에서 얻은 실제 메모리에 접근

이 두 과정을 거치는 것 또한 느리다. 그렇기에 페이지 테이블 자체를 캐싱하는 TLB기법이 생겼다.

* Valid: 메인 메모리에 캐싱되었는지(1), 디스크에 있는지(0)

* Dirty: 해당 데이터가 수정되었는지(1), 아닌지(0)

* Ref: 해당 데이터가 최근에 쓰인건지(1), 아닌지(0) (아니면 교체 대상임)

참고로 Dirty를 사용하는 이유는, 가상 메모리가 사용하는 disk는 느리기에 데이터를 바로 반영하지 않고,

replace될 때만 데이터를 disk에 반영해야하기 때문에 dirty 상태인지 알아야 한다.

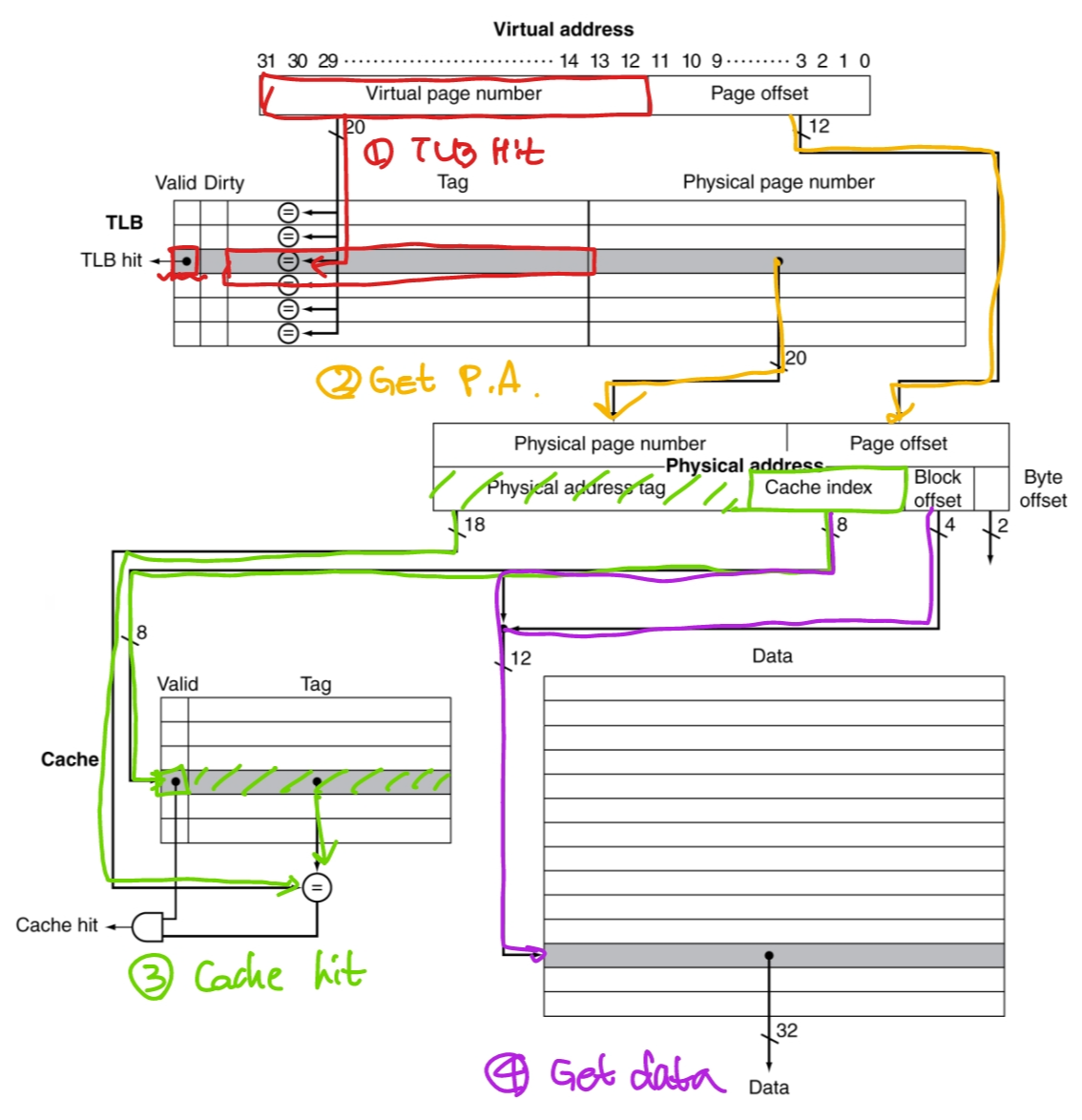

이제 TLB와 캐시 메모리와 연동되어서 동작하는 과정을 살펴보자.

(캐시 메모리와 관련된 내용은 Memory hierarchy 포스트에 있음)

<캐시 메모리 블럭 사이즈가 16word/block 인 경우이다> - 가상 주소를 받아, 이 데이터가 TLB에 캐싱되어있는지 확인한다.

- TLB = hit, 캐싱되어 있다면 physical page number를 알아내서 physical address를 얻는다.

- 해당 주소의 데이터가 캐싱되어있는지 확인한다.

- Cache = hit, 캐싱되어 있다면 offset값을 이용해 여려개의 word 중 필요한 데이터를 가져온다.

Trade-off

가상 메모리의 캐시 구현에 있어 고려해야 할 사항이다.

Design Change Effect on miss rate Negative performance effect 캐시 사이즈 키우기 Capacity miss를 줄일 수 있다.

(용량이 꽉 차서 방금 교체했는데 바로 다시 읽어야 할 상황이 줄어듦)Access time, cost가 증가함 Associativity 늘리기 Conflict miss를 줄일 수 있다.

(fully asso. 가 아닐 때, 특정 set을 차지하기 위해 경쟁하는 상황이 줄어듦)Access time이 증가함 Block 사이즈 키우기 Cold start miss를 줄일 수 있다.

(처음 한 블럭을 읽어도 한 번에 많은 데이터를 읽어오기에 첫 접근시 miss하는 상황이 줄어듦)한 번 miss하면 큰 블럭을 읽어야 하기에 miss penalty가 증가함.

block 사이즈가 크기 때문에 총 block 개수가 줄어들어 miss rate가 증가함.'대학 > 컴퓨터구조' 카테고리의 다른 글

Memory hierarchy (0) 2023.06.13 ILP - Instruction Level Parallelism (0) 2023.06.12 Hazard (0) 2023.06.12 CPU circuit - Pipeline (0) 2023.06.11 CPU circuit - Basic (1) 2023.06.11